# **RESEARCH ARTICLE**

#### SCALING CHALLENGES FOR ADVANCED TRANSISTOR DESIGN.

**M.Anil Kumar, Y.N.S.Sai Kiran, U.Jagadeesh, B.Balaram and M. Durga Prakash**<sup>\*</sup>. Department Of Ece., K L University, Greenfields, Vaddeswaram.

#### ..... Manuscript Info Abstract ..... We all are living in the digital world where we are going to use many Manuscript History devices which are fabricated using the CMOS technology. Due to the Received: 08 March 2017 constraint design of the circuits and long routing schemes we are Final Accepted: 12 April 2017 going to make the chip work a lot harder and it results in high power Published: May 2017 consumption. In order to reduce the power consumption we prefer to use certain techniques like usage of nano-materials instead of Key words:-Nanowire, FET, Threshold voltage, conventional Poly-Silicon. In this technique we are interested to Drain Current, SILVACO, Poly Aniline, modify certain conditions which results in generation of a new kind of Pedot Pss, Gate length variations. technology which results in low power consumed, high speed circuits and devices which make a new way in the world of electronics. To reduce the power consumption of transistor i.e., when compared with ordinary transistor we has to reduce the power consumption as well as

ordinary transistor we has to reduce the power consumption as well as the power dissipation <sup>[6]</sup>. So we propose the application of nanomaterials which have high conductivity as well as low – power dissipation which can be employed in design of Transistors of various technologies (like 200nm., 100nm., 50nm. etc.,).

Copy Right, IJAR, 2016,. All rights reserved.

Introduction:-

CMOS Technology is facing a lot of problems over the last 30 years .In conventional MOSFET we have certain electrostatic limitations like source to drain tunneling, carrier mobility, static leakages etc., <sup>[1] [5]</sup>. As the size of nanomaterials is very small we can use a more number of transistors on a single chip so that size of the chip is reduced its additional features which can relatively reduce the complex fabrication into simple steps of fabrication so device and circuit developers are using this type of devices and also can use different types of materials used to make these type of materials at low cost <sup>[2]</sup>.

For an Ultra-small MOSFET we have to face several problems like high leakage current, high threshold voltage, high inter-connective capacitances, static leakages etc., all these problems can damage the MOSFET by reducing its performance <sup>[1] [5]</sup>.

In the VLSI industry it is critically necessary to have a device which has low power dissipation and has high performance along with long time durability. In order to achieve such characteristic features in a real time operation scenario it will be a hard tenacious task <sup>[11]</sup>. More in the present modern world the electronic device must have low response time along with low power consumption provided the cost of the device must be in a nominal range <sup>[7]</sup>. Using a conventional MOSFET device can no longer sustain such a modern day challenge. So if we use Nano-Materials we can meet the modern day challenge <sup>[3][4]</sup>.

In this paper we had replaced the Poly-Silicon material present on the Gate Terminal of the MOSFET device with different Nano-Materials like Si (Silicon Nano-Wires), ZnO (Zinc Oxide Nano-Wires), CSi (Carbon-Silicon or Silicon Carbide Nano-Wires), Pani (Poly-Aniline Nano-wires), Pedot:pss (Poly Styrene Sulfonate Nano-Wires)<sup>[8][9]</sup>.

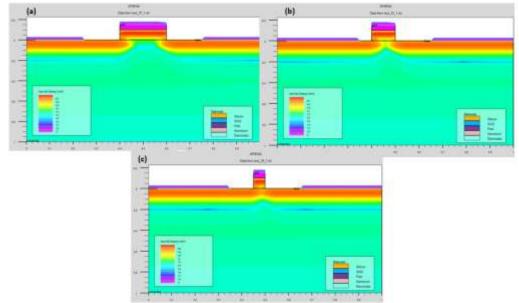

Fig. 1:- Schematic of Nano Wire FET.

In this paper we reduced the gate length i.e, the size of gate is reduced from 200 nm to 50 nm, for all the materials (Poly-Silicon, SiO, ZnO, CSilicon, Pani, PedotPss) and their characteristic parameters like drain current, threshold voltage are extracted.

## Literature Survey:-

#### Design Methodology:-

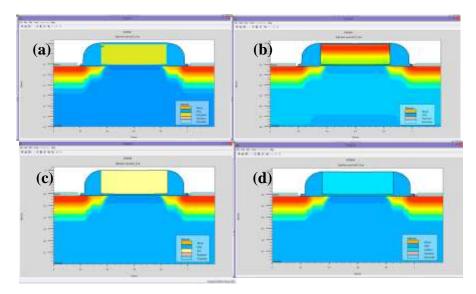

In this paper we have used Silvaco Software for the design of the Nano-Wire FET. Initially we have designed a Nano-Wire FET of 200 nm in size. There are two different design styles which are represented in figures (2) & (3).Basically first we will mention the X co-ordinates and Y co-ordinates in the software which will guide the software to lay the Silicon Wafer to those desired Co-ordinates. Later the Sio (Silicon Oxide) material is laid <sup>[10]</sup>.

Then it is etched to form gate, source and drain terminals. Later, respective impurities are doped accordingly. After doping process is completed, the respective Gate material is laid. Since we have used different gate materials like Pani, Pedot:Pss, Si, ZnO, CSilicon,Polysilicon etc., each material is laid one at a time. Now the Gate material is etched at source and drain terminals. Based on the required sizes i.e. based on required gate lengths it is etched once again <sup>[10]</sup>.

Now over the Gate terminal once again the Silicon Dioxide  $(SiO_2)$  material is laid and is etched off at source and drain terminals. Now Aluminum metal is laid which forms the respective metal contacts for the so designed FET <sup>[10]</sup>.

Fig 2:- Schematic of different Nano Wire MOSFETs: a) PolySilicon ; b) Silicon Nano Wire ; c) Zinc Oxide Nano Wire ; d) Carbon Silicon; e) Poly Aniline; f)PEDOT:PSS materials in Silvaco Software.

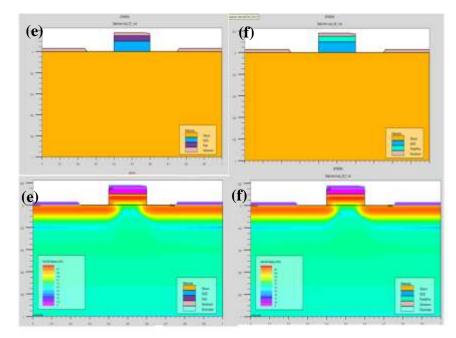

**Fig 3(a):-** Schematic of different gate sizes of Nano Wire MOSFETs: a) 200 nm; b) 100nm; c) 50nm technologies in Silvaco Software (No Doping Concentrations are shown)

Fig 3(b) :- Schematic of different gate sizes of Nano Wire MOSFETs: a) 200 nm; b) 100nm;c) 50nm technologies in Silvaco Software (Doping Concentrations are shown)

#### **Equations:-**

Saturation region drain current:  $I_d=(\mu c_{ox} \omega)/(2L)*(V_{gs}-V_t)^{2*}(1-V_{ds}/V_A)$ ;  $V_{ds}>=V_{gs}-V_t$ Ohmic region drain current:  $I_d=(\mu c_{ox} \omega)/(2L)*[2*(V_{gs}-V_t)V_{ds} - V_{ds}^2]*(1-V_{ds}/V_A)$ ;  $V_{ds}< V_{gs}-V_t$ Oxide capacitance:  $c_{ox} > \varepsilon_{ox}/t_{ox}$ Transconductance:  $g_m>(\mu c_{ox} \omega/L)(V_{gs}-V_t)$ Output resistance:  $R_o=|V_A|/I_{do}$ Input capacitance:  $C_{in}>C_{gs}+C_{gd}=C_{ox}L\omega$ Transition frequency:  $F_c>g_m/(2*pi*C_{in})$ Surface mobility holes:  $\mu>200cm^2/V$ -s where Drain current =  $I_d$ ; Oxide capacitance =  $c_{ox}$ ; Transconductance =  $g_m$ ; Output resistance =  $R_o$ ; Input capacitance =

Drain current =  $I_d$ ; Oxide capacitance =  $c_{ox}$ ; Transconductance =  $g_m$ ; Output resistance =  $R_o$ ; Input capacitance =  $C_{in}$ ; Transition frequency =  $F_c$ ; Electronic Field Strength in Oxide =  $\varepsilon_{ox}$ ; Gate to Source Voltage =  $V_{gs}$ ; Drain to Source Voltage =  $V_{ds}$ ; Thicknessof Oxide Layer = $t_{ox}$ ; Threshold Voltage =  $V_t$ .

#### **Results and Discussions:-**

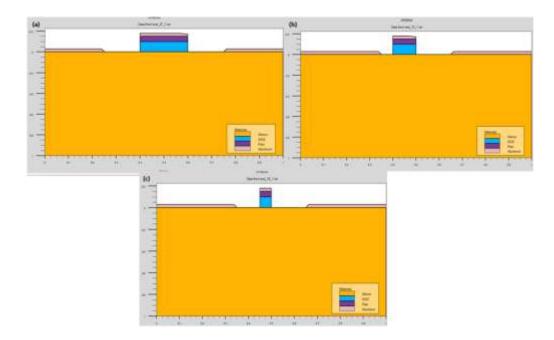

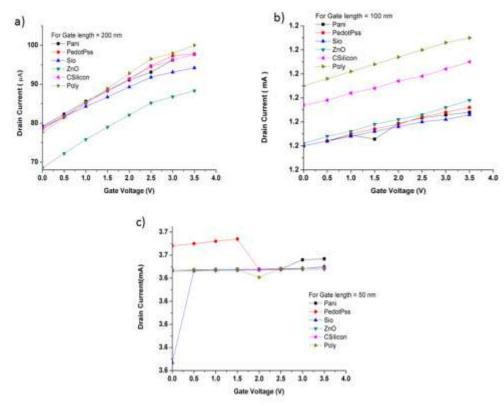

After designing the FET the  $I_{ds}$  Vs.  $V_{gs}$  parameters for different gate materials of different gate lengths has been plotted as shown in figure (4).

The  $I_{ds}$  Vs.  $V_{gs}$  parameter for various materials of 200 nm is shown in figure (4.a). From the figure we can understand that ZnO (Zinc Oxide) material has low drain current .

Similarly for 100 nm technology shown in figure (4.b) the  $I_{ds}$  Vs.  $V_{gs}$  parameter has been plotted. From this we can understand that PAni (PolyAnniline) has least drain current value.

For 50 nm technology shown in figure (4.c) the  $I_{ds}$  Vs.  $V_{gs}$  parameter is taken and is represented as a graph, from which we can conclude that ZnO is ideal material to be used in this technology as it has least drain current parameter.

Fig 4:-  $I_{ds}$  Vs.  $V_{gs}$  Characteristics for Channel lengths a) 200 nm; b) 100 nm; c) 50 nm gate channel lengths (for constant  $V_{ds} = 0.1$  Volts)

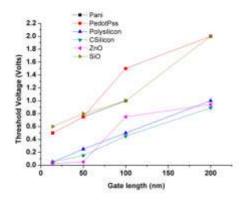

Similarly after plotting the Threshold Voltage values we can observe that the ZnO material has least threshold voltage value at 50 nm technology while CSilicon has low threshold voltage for 100nm; 200 nm technologies. But as the current trend is all about scaling down of IC's it will be ideal to use the ZnO nano material in the design of FET having less gate lengths.

Similarly if we consider the Polymeric compounds PAni (Poly Anniline) has least threshold voltage value but not a good one when compared with ZnO material.

| Gate Length | Threshold  | Threshold  | Threshold  | Threshold  | Threshold  | Threshold  |

|-------------|------------|------------|------------|------------|------------|------------|

|             | voltage of |

|             | Pani       | PedotPss   | Pani       | Csilicon   | ZnO        | SiO        |

| Nm          | Volts      |            |            |            |            |            |

| 50          | 0.75       | 0.75       | 0.25       | 0.15       | 0.05       | 0.8        |

| 100         | 1          | 1.5        | 0.5        | 0.45       | 0.75       | 1          |

| 200         | 2          | 2          | 1          | 0.89       | 0.94       | 2          |

Fig 5 Threshold Voltages for different Gate Materials and for different Gate lengths.

Fig 6:- Threshold Voltages for different Gate Materials and for different Gate lengths.

### **Conclusion:-**

From  $I_{gs}$  Vs.  $V_{gs}$  THRESHOLD VALUES,  $I_{ds}$  Vs.  $V_{ds}$  CURVE VALUES, Gate channel length effects, i.e. figures(4),(5),(6) we can observe that the FET designed using the Poly Aniline Nano-wire Material has less drain current, drain voltage, low threshold voltage, when compared with other polymeric compounds, while overall performance parameters are best for Zinc-Oxide (ZnO) material when compared with all the above mentioned materials.

### **References:-**

- High Performance Silicon Nanowire Field Effect Transistors Yi Cui, Zhaohui Zhong, Deli Wang, Wayne U. Wang, and Charles M. Lieber, Department of Chemistry and Chemical Biology, and Division of Engineering and Applied Science, Harvard University, Cambridge, Massachusetts 02138 Received November 1, 2002 (NANO LETTERS 2003 VOL 3, NO-2, 149-152.

- 2. H. S. P. Wong, "Beyond the conventional transistor," Solid State Electronics, vol. 49, pp. 755-762, May 2005 s

- 3. J. T. Park, J. P. Colinge, "Multiple-gate SOI MOSFETs: device design guidelines," IEEE Trans. Electron Devices, Vol. 49, No. 12, pp. 2222 -2229, Dec. 2002.

- 4. IWAI Hiroshi, Natori Kenji, SHIRAISHI Kenji, IWATA Jun-ichi, OSHIYAMA Atsushi, YAMADA Keisaku, OHMORI Kenji, KAKUSHIMA Kuniyuki & AHMET Parhat, "SI Nanowire FET and its modeling", "Science China", MAY 2011, Vol. 54, No-5:1004-1011, DOI:10,1007/s11432-011-4220-0.

- Bipul C.Paul, Ryan Tu, Shinobu Fujita, Masaki Okajima, Thomas H Lee , Yoshio Nishi, "An Analytical Compact Circuit Model for Nano Wire FET", IEEE Transactions on Electronic Devices, Vol. 54, No.7, July 2007.

- 6. Variability Study of Si Nano-Wire FETs with different junction gradients by Jun-Sik Yoon, Kihyun Kim, Taiuk Rim and Chang-Ki Baek, AIP Advances 6,015318 (2016); doi :10.1063/1.4941351.

- R. Chau, S. Datta, and A. Majumdar, "Opportunities and challenges of III-V nano-electronics for future highspeed, low-power logic applications," in Proc. IEEE Compound Semiconductor Integr. Circuit Symp., Oct./Nov. 2005, pp. 17–20.

- 8. Electronics of Conjugated Polymers : PolyAniline by Kerileng M. Molapo, Peter M. Ndangili, Rachel F. Ajayi, Gcineka Mbambisa, Stephen M. Mailu, Njagi Njomo, Milua Masikini, Priscilla Baker and Emmanuel I. Iwuoha , International Journal Of ELECTROCHEMICAL SCIENCE (2012) 11859-11875.

- Dr. Bowler, "Atomic-Scale Nano-Wires : Physical & Electronic Structure", J. Phys. cond. Matt., Vol. 16 PP R 721 - R754,2004.

- 10. "ATLAS User's Manual Volume I, Silvaco International", March 2007

- 11. Vijay Sai Patnaik, Ankit Gheedia and M.Jagadeesh Kumar,"3D Simulation of Nano-Wire FET's using Quantum Models", The Simulation Standard : JULY, AUGUST, SEPTEMBER 2008.