# **RESEARCH ARTICLE**

## TUNABLE MIXED DECIMATION MULTIPATH DELAY FEEDBACK FOR RADIX 2<sup>K</sup> FFT.

#### G. Ganga bhavani<sup>1</sup> and Dr. G. r. l. v. n srinivasa raju<sup>2</sup>.

.....

- 1. Pg scholar, dept. Of ece, shri vishnu engg. College for women, bhimavaram.

- 2. Professor & head, dept. Of ece, shri vishnu engg. College for women, bhimavaram.

# Manuscript Info

#### Abstract

Manuscript History

Received: 14 April 2018 Final Accepted: 16 May 2018 Published: June 2018

#### Keywords:-

Decimation in Frequency (DIF), Decimation in Time (DIT), Multipath Delay Feedback (MDF), Mixed Decimation Multi Path Delay Feedback (M<sup>2</sup>DF), Pipelined-Parallel Architecture. The Decimation Multipath Delay Feedback ( $M^2DF$ ) is a technique for the radix 2<sup>k</sup> FFT, which eliminates the stand by time of arithmetic modules in computing units. In this paper tunable  $M^2DF$  architecture is proposed. In this, tunable arithmetic units are utilized in place of conventional arithmetic units to overcome the under utilization of arithmetic units in conventional  $M^2DF$  architecture. The results show that, the tunable  $M^2DF$  technique utilizes the lesser number of LUTs and slice registers than the conventional  $M^2DF$  technique. In addition, the proposed technique having advantage of high throughput with reduced delay and area compared with conventional  $M^2DF$ .

.....

Copy Right, IJAR, 2018,. All rights reserved.

### Introduction:-

Fast Fourier Transform (FFT) is mostly used algorithm for Discrete Fourier Transform computation in the field of signal processing. The area efficient and high performance FFT implementation throws a challenge on the designers. Hardware designers are putting effort to design effectual architectures for the computation of the FFT to meet required specificatons and real-time fulfillment of present applications. Various techniques have proposed over the years to tradeoff the area and performance of the FFT. Pipelined architectures [1] are extensively used because they will achieve more throughputs and small latencies relevant for today's applications to achieve small area and to dissipate less power. The single path delay commutator (SDC) [2] is the most popular technique in the serial input and serial output scenarios. Single path delay feedback (SDF) architecture is proposed to reduce the memory banks in the pipelines [3]. The SDF concept extended to radix 2 to radix  $2^k$  [4-6]. The high throughput requirements of communication services encouraged to multipath delay commutators [7] and multipath delay feedback (MDF) [8].

.....

The MDF structures are formed using multiple interconnected SDFs. The MDF scheme is utilized in various applications due to its efficient memory usage, but suffers from arithmetic resource utilization and it is rectified in  $M^2DF$  architecture [9], which utilizes the folding transformation technique for the significant reduction of arithmetic resources.

In this work, tunable M<sup>2</sup>DF architecture is proposed to further reduce the arithmetic operations in terms of number of LUTs and registers.

### Construction of M<sup>2</sup>DF Architecture:-

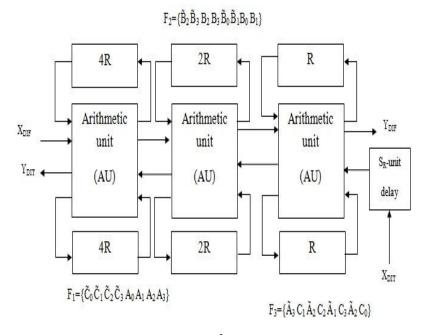

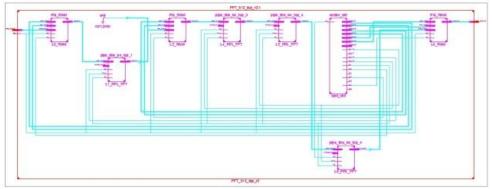

Design of parallel radix- $2^k$  FFT processor based on folding transformations to derive the folding matrices of DIF and DIT of SDF structures. The pipelined structure is rescheduled by incorporating DIF blocks into DIT blocks to form M<sup>2</sup>DF architecture from the SDF architecture. The M<sup>2</sup>DF mainly focus on horizontal processing in relevant to the hardware implantations and is shown in Fig.1

Address:- Pg scholar, dept. Of ece, shri vishnu engg. College for women, bhimavaram.

**Fig.1:-**M<sup>2</sup>DF Architecture

## Arithmetic Unit:-

The M<sup>2</sup>DF architecture mainly consists of control circuit and arithmetic unit and mathematics unit. Among them arithmetic unit plays an important role.

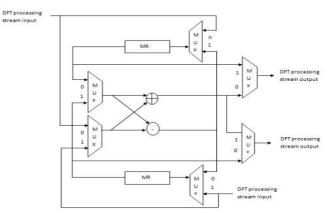

Fig. 2:-(a) Type I structure, complex adders are shared only

Fig. 2:-(b) Type II structure, both complex multipliers and complex adders are shared.

Conventionally two different structures are used. One is Type-I, In this adders are shared by means of streams and is shown in Fig. 2(a). Another type of arithmetic unit is Type – II, In this type adders and multipliers are reused to pick up the equipment effectiveness and is shown in Fig. 2(b).

#### Proposed M<sup>2</sup>DF Architecture using the tunable Arithmetic Unit:-

In the modified  $M^2DF$  architecture the conventional arithmetic units are modified using tunable arithmetic units, while maintaining the feedback structure of conventional architecture.

#### **Tunable Arithmetic unit:-**

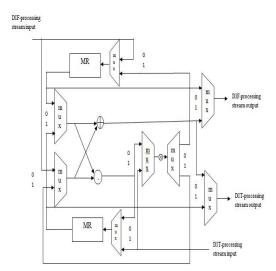

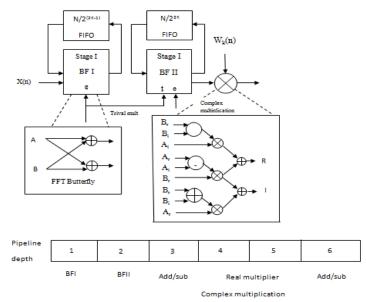

Fig. 3 shows the tunable arithmetic unit. In this 4-stage pipelined technique is adopted. This unit consists of 6 butterfly units and 3 complex multipliers. Compared to type I and type II AUs the proposed AU having high throughput and consumes less area. Due to the tunable arithmetic unit,

the inexact multiplier configurations have much higher sensitivities than the most of the inexact adder configurations and the pipelined technique is effectively utilized. Due to these advantages tunable arithmetic unit has a double impact on the quality of solutions.

Fig. 3;-Tunable Arithmetic unit

### Simulation Results:-

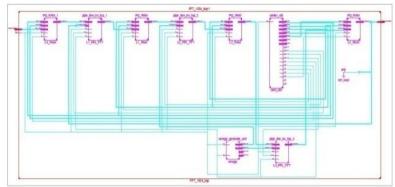

The simulation of the proposed  $M^2DF$  architecture and the conventional  $M^2DF$  architectures are carried out using Xilinx ISE 14.5.The simulation results are shown in Fig.4. (These Two parallel 512 point FFT designed using proposed tunable arithmetic unit).

| Name |    | е               | Value       |               | 1,482,530 ns                            | 1,482,540 ns     | 1,482,550 ns                            | 1,482,560 ns     | 1,482,570 ns  1,4                       | 482,5 |

|------|----|-----------------|-------------|---------------|-----------------------------------------|------------------|-----------------------------------------|------------------|-----------------------------------------|-------|

|      | 7  | data_out[31:0]  | 00000000000 | 0000000000000 | 000000000000000000000000000000000000000 | 0001001111011111 | 000000000000000000000000000000000000000 | 0001001111010100 | 000000000000000000000000000000000000000 | 01    |

|      | 16 | clk             | 1           |               |                                         |                  |                                         |                  |                                         |       |

|      | Q  | data_in[511:0]  | 00000000000 | 0000000000000 | 000000000000000000000000000000000000000 | 00000000000000   | 000000000000000000000000000000000000000 | 000000000000000) | 000000000000000000000000000000000000000 | 00    |

|      | Ę  | data_in_a(511:0 | 00000000000 | 0000000000000 | 000000000000000000000000000000000000000 | 00000000000000   | 000000000000000000000000000000000000000 | 000000000000000) | 000000000000000000000000000000000000000 | 00    |

|      |    | data_in_b(511:0 | 00000000000 | 0000000000000 | 000000000000000000000000000000000000000 | 00000000000000   | 000000000000000000000000000000000000000 | 000000000000000) | 000000000000000000000000000000000000000 | 00    |

|      | Q  | data_out_1[511  | 00000000000 | 0000000000000 | 000000000000000000000000000000000000000 | 00000000000000   | 000000000000000000000000000000000000000 | 000000000000000) | 000000000000000000000000000000000000000 | 00    |

|      |    | j i[31:0]       | 00000000000 | 0000000000000 | 000000000000000000000000000000000000000 | 0010000110001100 | 000000000000000000000000000000000000000 | 0010000110001101 | 000000000000000000000000000000000000000 | 10    |

Fig. 4:-Simulation results for Tunable M<sup>2</sup>DF Architecture for radix-2 512 point FFT.

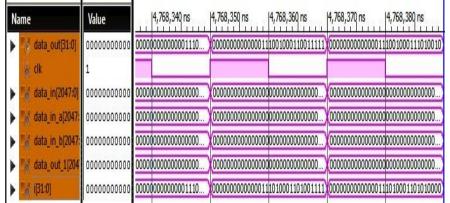

Here data\_in \_a and data\_in\_b are inputs indicates the iteration loops and data\_out is the required output. The corresponding RTL schematic of radix-2 two parallel 512 point FFT architecture is shown in Fig. 5.

Fig. 5:-RTL Schematic for tunable M<sup>2</sup>DF of radix-2 for 512 point FFT.

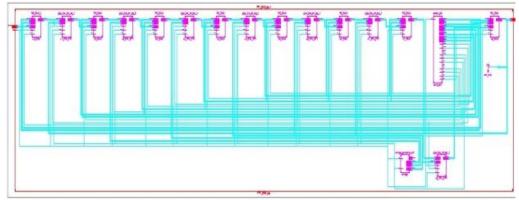

Similarly, the two parallel 1024 point FFT, two parallel 2048 point FFT and their RTL schematics are shown in Fig. 6 to Fig. 9.

| Name                | Value       |              | 4,766,600 ns  | 4,766,610 ns                            | 4,766,620 ns         |

|---------------------|-------------|--------------|---------------|-----------------------------------------|----------------------|

| 🕨 😽 data_out[31:0]  | 00000000000 | 000000000000 | 0001110010000 | 0000000000000000000011                  | 100 100000 10 10000) |

| 🔥 cik               | 1           |              |               |                                         |                      |

| 🕨 😽 data_in[1023:0] | 00000000000 | 00000000000  | 0000000000000 | 000000000000000000000000000000000000000 | 00000000000000)      |

| 🕨 😽 data_in_a[1023: | 00000000000 | 00000000000  | 0000000000000 | 000000000000000000000000000000000000000 | 00000000000000)      |

| 🕨 🕷 data_in_b[1023: | 00000000000 | 000000000000 | 0000000000000 | 000000000000000000000000000000000000000 | 00000000000000)      |

| 🕨 🕷 data_out_1(102  | 00000000000 | 00000000000  | 0000000000000 | 000000000000000000000000000000000000000 | 00000000000000)      |

| 🕨 📷 i[31:0]         | 00000000000 | 00000000000  | 0001110100010 | 000000000000000000000000000000000000000 | 1010001011111000)    |

Fig. 6:-Simulation results for tunable M<sup>2</sup>DF Architecture for radix-2 1024 point FFT.

Fig. 7:-RTL Schematic for tunable M<sup>2</sup>DF of radix-2 for 1024 point FFT

**Fig. 8:-**Simulation results for tunable M<sup>2</sup>DF Architecture for radix-2 2048 point FFT.

Fig.9:-RTL Schematic for M<sup>2</sup>DF of radix-2 2048 point Fast Fourier Transform.

| Configuration   | Structures                | Slice | Slice     | DSP48E1s | latency | throughput |

|-----------------|---------------------------|-------|-----------|----------|---------|------------|

|                 |                           | LUTs  | registers |          |         |            |

| Radix-2, 2/512  | M <sup>2</sup> DF FFT     | 2417  | 2077      | 24       | 524     | 612        |

|                 | Architecture              |       |           |          |         |            |

|                 | Tunable M <sup>2</sup> DF | 1140  | 1219      | 20       | 516     | 618        |

|                 | FFT Architecture          |       |           |          |         |            |

| Radix-2, 4/1024 | M <sup>2</sup> DF FFT     | 3154  | 3881      | 36       | 533     | 1196       |

|                 | Architecture              |       |           |          |         |            |

|                 | Tunable M <sup>2</sup> DF | 2060  | 2139      | 30       | 523     | 1238       |

|                 | FFT Architecture          |       |           |          |         |            |

Table 1:-Comparison of proposed structure with existing structures

| Radix-2, 8/2048               | M <sup>2</sup> DF FFT     | 6833  | 8860  | 84  | 542 | 2368 |

|-------------------------------|---------------------------|-------|-------|-----|-----|------|

| Kaulx-2, 8/2048               |                           | 0855  | 8800  | 84  | 342 | 2308 |

|                               | Architecture              | 4012  | 4670  |     | 520 | 2162 |

|                               | Tunable M <sup>2</sup> DF | 4012  | 4678  | 70  | 530 | 2463 |

|                               | FFT Architecture          |       |       |     |     |      |

| Radix-2 <sup>2</sup> , 2/512  | M <sup>2</sup> DF FFT     | 3345  | 2790  | 24  | 524 | 612  |

|                               | Architecture              |       |       |     |     |      |

|                               | Tunable M <sup>2</sup> DF | 1565  | 1780  | 24  | 513 | 613  |

|                               | FFT Architecture          |       |       |     |     |      |

| Radix- $2^2$ , $4/1024$       | M <sup>2</sup> DF FFT     | 3885  | 3112  | 36  | 533 | 1196 |

| ,                             | Architecture              |       |       |     |     |      |

|                               | Tunable M <sup>2</sup> DF | 2451  | 2696  | 32  | 519 | 1224 |

|                               | FFT Architecture          | _     |       | -   |     |      |

| Radix-2 <sup>2</sup> , 8/2048 | M <sup>2</sup> DF FFT     | 8753  | 5631  | 84  | 540 | 2368 |

|                               | Architecture              |       |       |     |     |      |

|                               | Tunable M <sup>2</sup> DF | 11207 | 14836 | 176 | 531 | 2398 |

|                               | FFT Architecture          |       |       |     |     |      |

| Radix-2 <sup>3</sup> , 2/512  | M <sup>2</sup> DF FFT     | 3436  | 3033  | 24  | 526 | 596  |

|                               | Architecture              |       |       |     |     |      |

|                               | Tunable M <sup>2</sup> DF | 1682  | 1717  | 24  | 518 | 613  |

|                               | FFT Architecture          |       |       |     |     |      |

| Radix-2 <sup>3</sup> , 4/1024 | M <sup>2</sup> DF FFT     | 5112  | 4225  | 48  | 536 | 1186 |

| ,                             | Architecture              |       |       |     |     |      |

|                               | Tunable M <sup>2</sup> DF | 3505  | 3992  | 44  | 528 | 1224 |

|                               | FFT Architecture          |       |       |     |     |      |

| Radix-2 <sup>3</sup> , 8/2048 | M <sup>2</sup> DF FFT     | 9062  | 10265 | 286 | 540 | 2372 |

|                               | Architecture              |       |       |     |     |      |

|                               | Tunable M <sup>2</sup> DF | 8446  | 8542  | 280 | 532 | 2398 |

|                               | FFT Architecture          |       |       |     |     |      |

|                               | FFI Architecture          |       |       |     |     |      |

# **Conclusion:-**

The Radix-2  $M^2DF$  based Fast Fourier Transform is most significant architecture in the DSP and various Communication systems. The FFT architecture used in the mixed decimation Multipath Delay feedback ( $M^2DF$ ) eliminates the stand by time of arithmetic modules in FB architectures by integrating Discrete In Time process into the Discrete In Frequency operated computing units. Still arithmetic resources are under utilization in order to overcome this problem uses the tunable FFT is used in the place of type I and type II of arithmetic units (AUs).

### **References:-**

- 1. M. Garrido, J. Grajal, M. A. Sanchez, and O. Gustafsson, "Pipelined radix-2<sup>k</sup> feed forward FFT architectures," IEEE Trans. Very Large Scale Integration (VLSI) Systems, vol. 21, no. 1, pp. 23–32, Jan. 2013.

- 2. Jian Wang, ChunlinXiong, Kangli Zhang, and Jibo Wei, "A Mixed-Decimation MDF Architecture for Radix-2<sup>k</sup> Parallel FFT" IEEE transactions on Very Large Scale Integration (VLSI) Systems, vol. 24, no. 1, january 2016.

- 3. A. Cortes, I. Velez, and J. F. Sevillano, "Radix r<sup>k</sup> FFTs: Matrical representation and SDC/SDF pipeline implementation," IEEE Trans. Signal Process., vol. 57, no. 7, pp. 2824–2839, Jul. 2009.

- 4. S. He and M. Torkelson, "Design and implementation of a I024-pointpipeline FFT processor," in Proc. IEEE Custom Integr. Circuits Conf., May 1998, pp. 131–134.

- 5. M. Ayinala, M. Brown, and K. K. Parhi, "Pipelined parallel FFT architectures via folding transformation," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 6, pp. 1068–1081, Jun. 2012.

- 6. K. K. Parhi, VLSI Digital Signal Processing Systems: Design and Implementation. Hoboken, NJ, USA: Wiley, 1999.

- 7. N. Li and N. P. Van Der Meijs, "A radix-22 based parallel pipeline FFT processor for MB-OFDM UWB system," in Proc. IEEE Int. SOC Conf., Sep. 2009, pp. 383–386.

- S.-N. Tang, J.-W. Tsai, and Z. Wang, X. Liu, B. He, and F. Yu.: A combined SDC-SDF architecture for normal I/O pipelined radix-2 FFT.IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, no. 5, pp. 973–977, May 2015.

- 9. S.N. Tang, C.H.Liao, and T.-Y. Chang, "An area- and energy-efficient multimode FFT processor for WPAN/WLAN/WMAN systems," IEEEJ. Solid-State Circuits, vol. 47, no. 6, pp. 1419–1435, Jun. 2012.

- 10. E. H. Wold and A. M. Despain, "Pipeline and parallel-pipeline FFT processors for VLSI implementations," IEEE Trans. Comput., vol. C-33, no. 5, pp. 414–426, May 1984.

- 11. J. E. Volder, "The CORDIC trigonometric computing technique," IRE Trans. Electron. Comput., vol. EC-8, pp. 330-334, Sept. 1959.

- K.-J. Yang, S.H.Tsai, and G. C. H. Huang, "MDC FFT/IFFT processor with variable length for MIMO-OFDM systems," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 21, no. 4, pp. 720–731, Apr. 2013.